## EECS 151/251 A Discussion 6 Feb 23, 2024

#### Content

- Transistors

- Pull up/ Pull down

- Circuit Layouts

- Problems

# Transistors

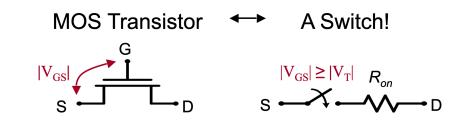

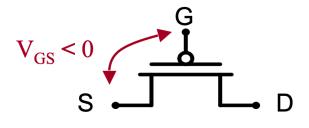

- NMOS and PMOS

- Bidirectional, but usually configured to work one way

- We abstract as a switch with resistance! There is actually some leakage current (I<sub>off</sub>) even when  $V_{GS} < V_T$

- What does raising/lowering  $V_{\rm T}$  do to  $I_{\rm off\ and}\ I_{\rm on}?$

- Resistance of transistor is not actually linear! But we approximate in this class

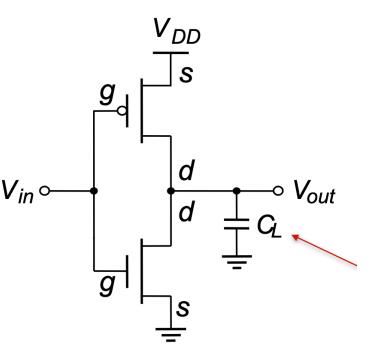

# **Connecting Transistors**

- C<sub>L</sub> models the capacitance of the entire system

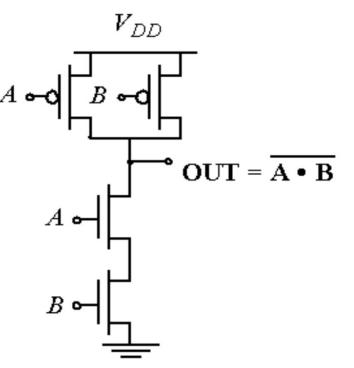

- What gate is this showing?

- Note that V<sub>out</sub> is either directly connected to ground or V<sub>DD</sub>, except for brief periods when switching

- Why does PMOS connect V<sub>DD</sub> while NMOS connects ground?

# Pull-Up vs Pull-Down

- Pull-Up: PMOS transistors that connect V<sub>DD</sub> to V<sub>out</sub>

- Pull-Down: NMOS transistors that connect ground to V<sub>out</sub>

- AND: Transistors in series

- OR: Transistors in parallel

- Pull–Up complements Pull–Down

# Pull-Up vs Pull-Down

- Pull-Up generates all 1s in truth table, Pull-Down generates all 0s

- Can you generate an AND gate (as a single gate)?

- Series connections in Pull-down are parallel in Pull-Up and vice versa (DeMorgan's)

- This ensures that pull-down and pull-up are never triggered at once!

#### **Static Gates vs Transmission Gates**

- Static Gates connect to V<sub>DD</sub> and ground

- Transmission gates connect A to B via idealized "switch'

- Can't connect too many transmission gates in a row. Why?

$$A \xrightarrow[en]{en} B$$

$$= if en == 1 then A connects to B$$

## **Circuit Layouts**

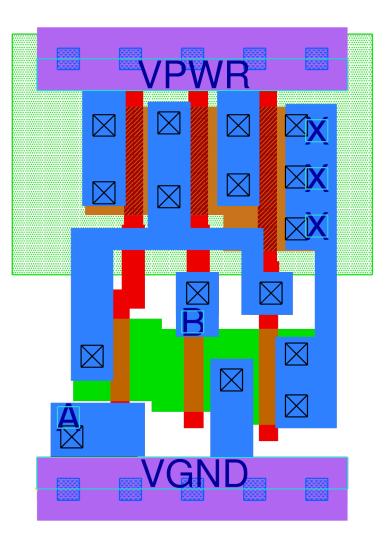

• What is this?

## **Circuit Layouts**

• AND Gate!

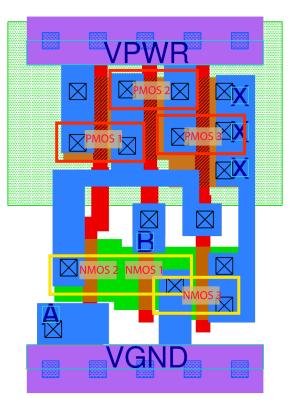

# **Circuit Layouts**

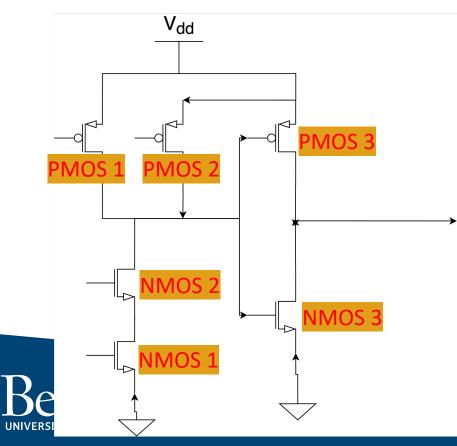

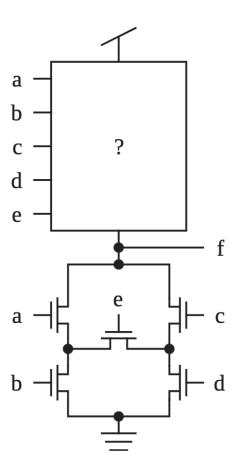

• What is this?

#### Problem 1

Complete the following CMOS schematic with inputs a, b, c, d, e and output f. Also, write a Boolean expression of the output f.

## Solution

#### Solution:

Function:

$$f = (ab + cd + aed + bce)' \tag{1}$$

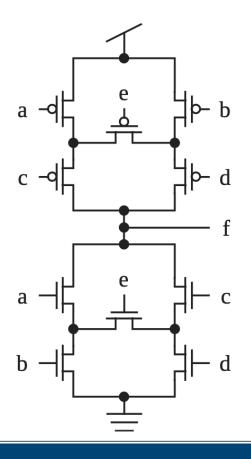

#### Problem 2

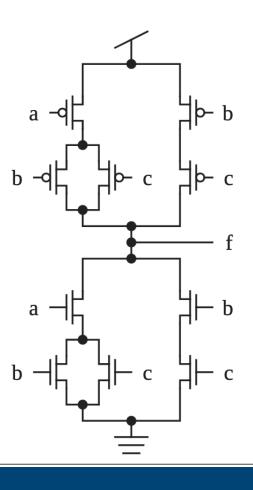

Write a CMOS schematic for f = a'b' + b'c' + c'a'.

#### Solution

Function:

$$f' = (a+b)(b+c)(c+a) = ab + bc + ca = a(b+c) + bc$$

(2)

Schematic: