## EECS 151/251A Discussion 2

Feburary 2, 2024

## **Problem 1: LUTs and Functions**

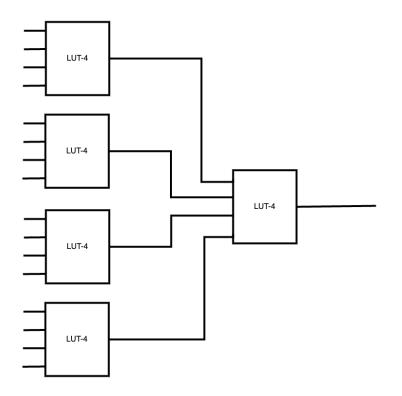

Lookup Tables (LUTs) are the fundamental building blocks of FPGA architectures. A LUT-N can implement **any** N input logic function (ex. a LUT-4 can implement any logic function with four logical inputs). On an FPGA, LUTs can be connected together through special routing to implement functions with even more inputs. Consider the following arrangement of five LUT-4 blocks:

How many logic functions can this chain of LUT-4's implement?

## Problem 2: Self Starting Ring Counter

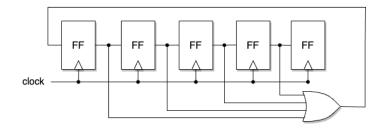

A ring counter is a special counter composed of flip-flops daisy-chained together to form a shift register and the output of the last flip-flop is connected to the output of the first. Below is a variant of self starting ring counter. (**Note:** the last flip-flops output is not the input to the first, but it's close enough to call it a ring counter :-)). It is self starting because there is no reset. The counter will reset itself! The counter is read out such that the first register is the LSb of the count value.

- 1. How does this self-initialize itself?

- 2. What type of counter is this?

- 3. Assume the register are initialized as 0, 1, 0, 1, 0. Create a table showing clock cycle, input to the chain, value of each register. Provide a waveform diagram for the first 10 cycles after initialization.

- 4. How does the circuit behave in steady state (steady state means after hundreds of cycle)?

- 5. This behavior can be create using a regular incrementing counter and a decoder. Write Verilog for this implementation.

## Problem 3: Bit-Stream Reverse Engineering

Imagine you obtained a bit-stream from somewhere and want to figure out what it is.

- (a) The bit-stream is 0x1777A5A5965A9696. This bitstream is fed in from right to left (i.e. 6 is fed first and 1 is fed last).

- (b) Every LUT in the FPGA has N inputs (the value of N is part of the mystery). The LUTs are numbered 0, 1, 2, ....

- (c) Each LUT has an output labeled  $y_i$  and inputs labeled  $x_{i_j}$ , where *i* is the LUT number and *j* is the input number.

- (d) For programming, the LUTs are connected in a shift register. The bit-stream will be shifted in from LUT0 and then pushed to the subsequent LUTs. (This implies that the left most 1 must be part of the function for LUT0.)

- (e) The shift register is ordered in the ascending order of input for each LUT. That is, the first register stores the output for an input 00...0, the second register stores the output for an input 00...01 (only  $x_{i_0}$  is 1), and so on. (This implies that if N = 2, LUT0 programmed with 1 works as an AND gate.)

- (f) One of the LUTs is programmed as a 2-input gate. Furthermore, it is the only LUT programmed as a 2-input gate.

Answer the following questions:

- 1. How many LUTs would the above bit stream program?

- 2. Write down the function of each LUT in Boolean expression (no need to simplify but notice there are some patterns that can be concisely expressed with XORs).