EECS151/251A

Fall 2024

Digital Design and Integrated Circuits

Instructor:

John Wawrzynek

Lecture 21: Adders

#### **Announcements**

- □ Homework 10 posted <u>due next Wednesday</u>

- □ 2 more weeks of lecture (including this week)

- □ Next week Monday guest lecture: Sandesh Bharadwaj, from Apple

- □ 1 more homework exercise

#### **Outline**

- □ "tricks with trees"

- □ Adder review, subtraction, carryselect

- □ Carry-lookahead

- □ Bit-serial addition, summary

#### **Tricks with Trees**

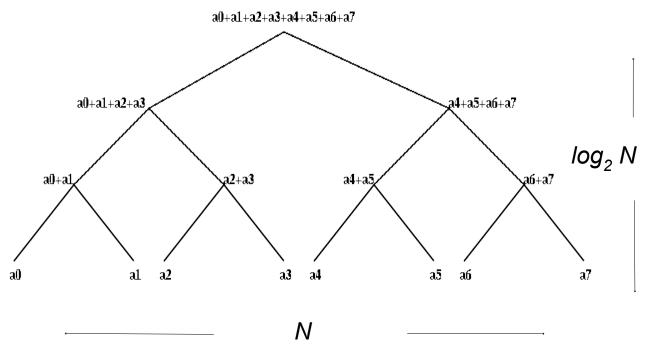

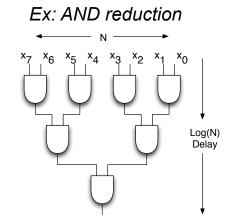

#### Reductions with Trees - Review

If each node (operator) is k-ary instead of binary, what is the delay?

Demmel - CS267 Lecture 6+

### Trees for optimization

- □ What property of "+" are we exploiting?

- □ Other associate operators? Boolean operations? Division? Min/Max?

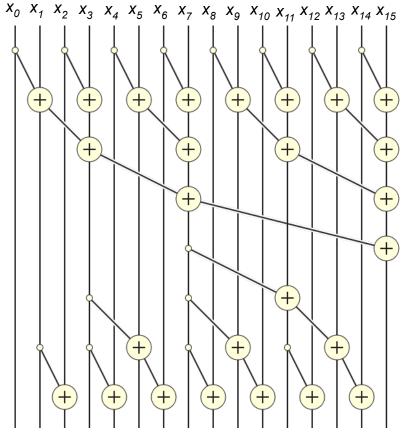

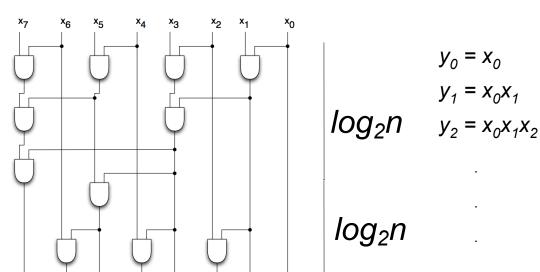

#### Parallel Prefix, or "Scan"

□ If "+" is an associative operator, and  $x_0,...,x_{p-1}$  are input data then *parallel prefix* operation computes:

$$x_0, x_0 + x_1, x_0 + x_1 + x_2, ...$$

$y_j = x_0 + x_1 + ... + x_j$  for  $j=0,1,...,p-1$

$y_0$   $y_1$   $y_2$   $y_3$   $y_4$   $y_5$   $y_6$   $y_7$   $y_8$   $y_9$   $y_{10}$   $y_{11}$   $y_{12}$   $y_{13}$   $y_{14}$   $y_{15}$

#### Adder review, subtraction, carry-select

### 4-bit Adder Example

Motivate the adder circuit design by hand addition:

□ Add a0 and b0 as follows:

| a | b | r | С | <b>T</b> | carry to next |

|---|---|---|---|----------|---------------|

| 0 | 0 | 0 | 0 |          | stage         |

| 0 | 1 | 1 | 0 |          | •             |

| 1 | 0 | 1 | 0 |          |               |

| 1 | 1 | 0 | 1 |          |               |

$$r = a XOR b = a \oplus b$$

$c = a AND b = ab$

Add a1 and b1 as follows:

| ci | а | b | r | CO |

|----|---|---|---|----|

| 0  | 0 | 0 | 0 | 0  |

| 0  | 0 | 1 | 1 | 0  |

| 0  | 1 | 0 | 1 | 0  |

| 0  | 1 | 1 | 0 | 1  |

| 1  | 0 | 0 | 1 | 0  |

| 1  | 0 | 1 | 0 | 1  |

| 1  | 1 | 0 | 0 | 1  |

| 1  | 1 | 1 | 1 | 1  |

$$r = a \oplus b \oplus c_i$$

$co = ab + ac_i + bc_i$

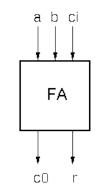

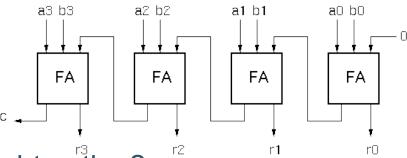

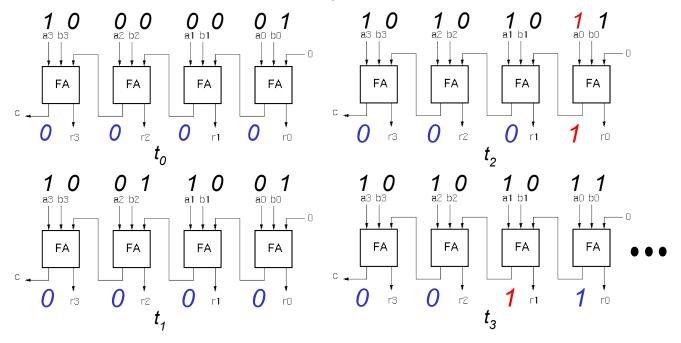

### Carry-ripple Adder Revisited

#### □ Each cell:

$$r_i = a_i \oplus b_i \oplus c_{in}$$

$$c_{out} = a_i c_{in} + a_i b_i + b_i c_{in} = c_{in} (a_i + b_i) + a_i b_i$$

"Full adder cell"

#### □ 4-bit adder:

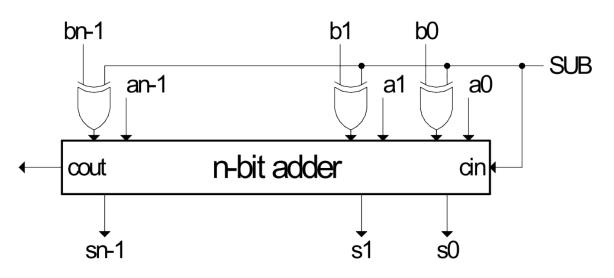

☐ What about subtraction?

#### Subtractor/Adder

$$A - B = A + (-B)$$

How do we form -B?

- 1. complement B 2. add 1

### Delay in Ripple Adders

□ Ripple delay amount is a function of the data inputs:

□ However, we usually only consider the worst case delay on the critical path.

There is always at least one set of input data that exposes the worst case delay.

### Adders (cont.)

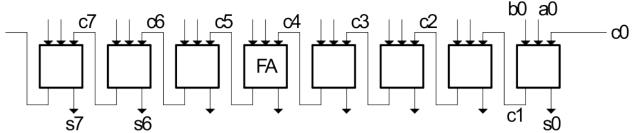

#### Ripple Adder

Ripple adder is inherently slow because, in worst case s7 must wait for c7 which must wait for c6 ...

$T \alpha n$ ,  $Cost \alpha n$

How do we make it faster, perhaps with more cost?

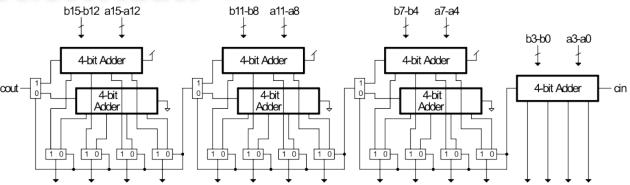

## Carry Select Adder

$$COST = 1.5 * COST_{ripple\_adder} + (n/2 + 1) * COST_{MUX}$$

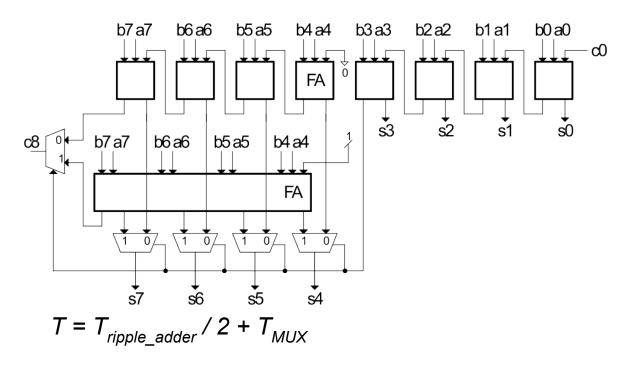

## Carry Select Adder

Extending Carry-select to multiple blocks

- □ What is the optimal # of blocks and # of bits/block?

- If blocks too small delay dominated by total mux delay

- If blocks too large delay dominated by adder ripple delay

$$\sqrt{N}$$

stages of  $\sqrt{N}$  bits

$$T \alpha \text{ sqrt}(N)$$

,

Cost  $\approx 2 \text{*ripple} + \text{muxes}$

Carry Select Adder

Compare to ripple adder delay:

$$T_{total} = 2 \text{ sqrt(N)} T_{FA} - T_{FA}$$

assuming  $T_{FA} = T_{MUX}$

For ripple adder  $T_{total} = N T_{FA}$

"cross-over" at N=3, Carry select faster for any value of N>3.

- □ Is sqrt(N) really the optimum?

- From right to left increase size of each block to better match delays

- Ex: 64-bit adder, use block sizes [12 11 10 9 8 7 7], the exact answer depends on the relative delay of mux and FA

(note: one less block than sqrt(N) solution)

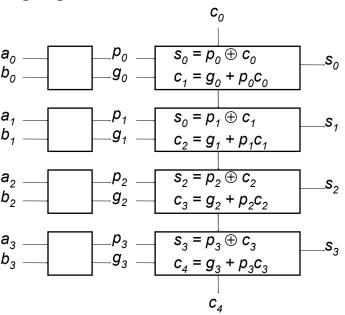

#### Carry-lookahead and Parallel Prefix

- □ How do we arrange carry generation to be associative?

- □ Reformulate basic adder stage:

| a b c $_{i }$ | $C_{i+1}$ | S     |                        |

|---------------|-----------|-------|------------------------|

| 000           | 0         | 0     | carry "kill"           |

| 001           | 0         | 1     | $k_i = a_i' b_i'$      |

| 010           | 0         | 1     |                        |

| 011           | 1         | 0     | carry "propagate"      |

| 100           | 0         | 1     | $p_i = a_i \oplus b_i$ |

| 101           | 1         | 0     | , i i i                |

| 110           | 1         | 0     | carry "generate"       |

| 111           | 1         | 1     |                        |

| 110           | 1 1       | 0 0 1 |                        |

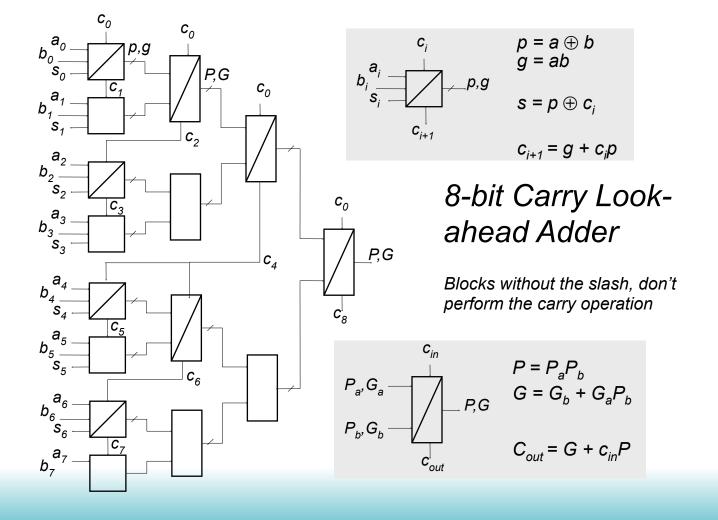

$$c_{i+1} = g_i + p_i c_i$$

$$s_i = p_i \oplus c_i$$

□ Ripple adder using p and g signals:

$$p_i = a_i \oplus b_i$$

$$g_i = a_i b_i$$

$\square$  So far, no advantage over ripple adder: T  $\alpha$  N

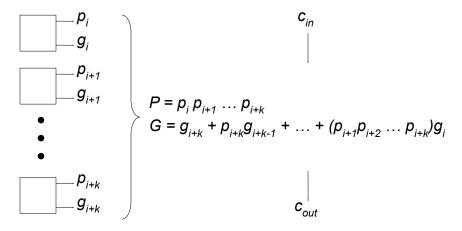

□ "Group" propagate and generate signals:

- □ P true if the group as a whole propagates a carry to c<sub>out</sub>

- □ G true if the group as a whole generates a carry

$$c_{out} = G + Pc_{in}$$

□ Group P and G can be generated hierarchically.

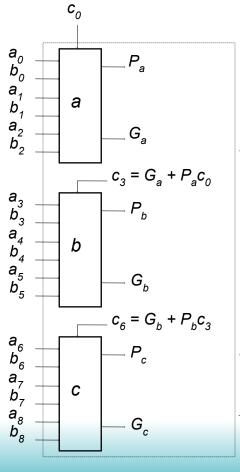

9-bit Example of hierarchically generated P and G signals:

$$P = P_a P_b P_c$$

$$G = G_c + P_c G_b + P_b P_c G_a$$

$$c_9 = G + Pc_0$$

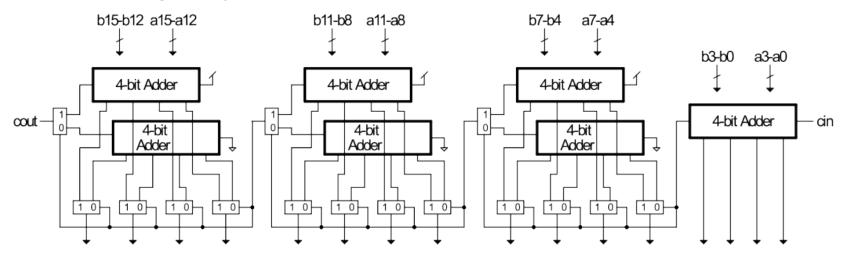

## 8-bit Carry Look-ahead Adder with 2-input gates.

#### Parallel-Prefix Review

Lowest delay for a reduction is a balanced tree.

- In cases where all intermediate values are required,

- one way is to use "Parallel Prefix":

y<sub>7</sub>

Can carry generation be made to be a kind of "reduction operation"?

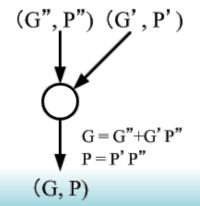

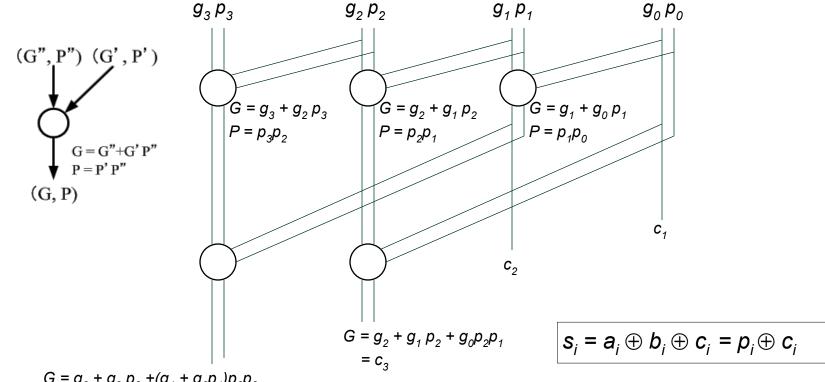

#### Parallel-Prefix Carry Look-ahead Adders

□ Ground truth specification of all carries directly (no grouping):

$$c_0 = 0$$

$c_1 = g_0 + p_0 c_0 = g_0$

$c_2 = g_1 + p_1 c_1 = g_1 + p_1 g_0$

$c_3 = g_2 + p_2 c_2 = g_2 + p_2 g_1 + p_1 p_2 g_0$

$c_4 = g_3 + p_3 c_3 = g_3 + p_3 g_2 + p_3 p_2 g_1 + p_4 p_3 p_2 g_0$

$$c_{i+1} = g_i + p_i c_i$$

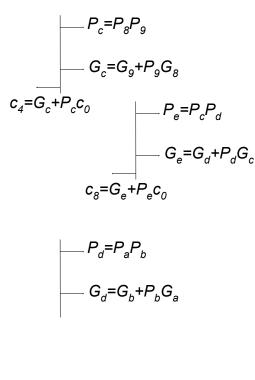

Binary (G, P) associative operator

Assumes carry signal moving from right to left. Not communitive.

Can be used to form all carries!

Use binary (G,P) operator to form parallel prefix tree

### Parallel Prefix Adder Example

$$G = g_3 + g_2 p_3 + (g_1 + g_0 p_1) p_3 p_2$$

=  $g_3 + g_2 p_3 + g_1 p_3 p_2 + g_0 p_3 p_2 p_1$

=  $c_4$

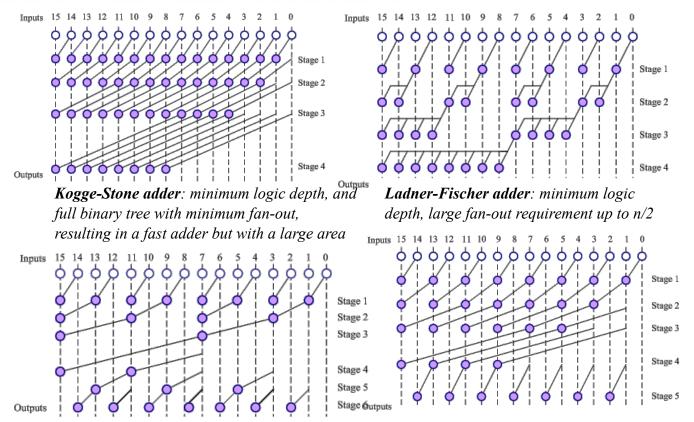

#### Other Parallel Prefix Adder Architectures

**Brent-Kung adder:** minimum area, but high logic depth

Han-Carlson adder: hybrid design combining stages from the Brent-Kung and Kogge-Stone adder

## Carry look-ahead Wrap-up

- □ Adder delay O(logN).

- □ Cost?

- □ Can be applied with other techniques. Group P & G signals can be generated for sub-adders, but another carry propagation technique (for instance ripple) used within the group.

- For instance on FPGA. Ripple carry up to 32 bits is fast, CLA used to extend to large adders. CLA tree quickly generates carry-in for upper blocks.

# Bit-serial Addition, Adder summary

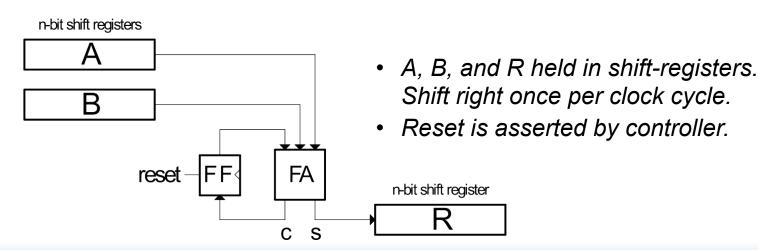

#### Bit-serial Adder

- □ Addition of 2 n-bit numbers:

- takes n clock cycles,

- uses 1 FF, 1 FA cell, plus registers

- the bit streams may come from or go to other circuits, therefore the registers might not be needed.

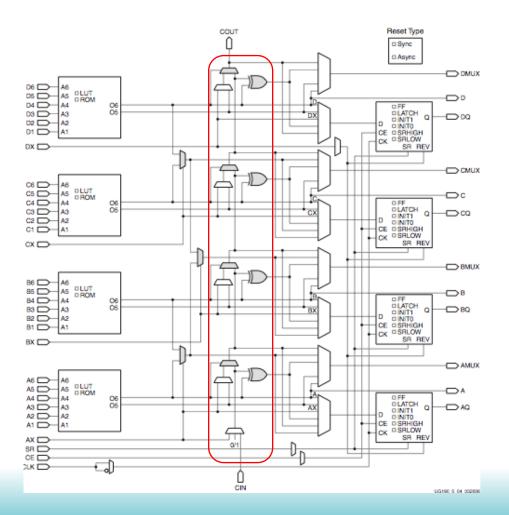

#### Adders on FPGAs

- Dedicated carry logic provides fast arithmetic carry capability for highspeed arithmetic functions.

- On Virtex-5

- Cin to Cout (per bit)

delay = 40ps, versus

900ps for F to X delay.

- 64-bit add delay =

2.5ns.

#### Adder Final Words

| Туре            | Cost  | Delay      |

|-----------------|-------|------------|

| Ripple          | O(N)  | O(N)       |

| Carry-select    | O(N)  | O(sqrt(N)) |

| Carry-lookahead | O(N)  | O(log(N))  |

| Bit-serial      | 0(1)* | O(N)       |

\* not counting shift registers

- $\Box$  Dynamic energy per addition for all of these is O(n).

- "O" notation hides the constants. Watch out for this!

- □ The "real" cost of the carry-select is at least 2X the "real" cost of the ripple. "Real" cost of the CLA is probably at least 2X the "real" cost of the carry-select.

- □ The actual multiplicative constants depend on the implementation details and technology.

- □ FPGA and ASIC synthesis tools will try to choose the best adder architecture automatically assuming you specify addition using the "+" operator, as in "assign A = B + C"